# Joining BCD encoding and 19-bit (?!) graphics addressing

A quick look at a few blocks of code from last month's "balls" demo and then... RTC and Interrupts use

## **Binary Coded Decimal (again)**

Discussed prior, the BCD mode of the 6502 CPU gives the programmer an efficient and low-touch method to perform arithmetic on base-10 numbers and does so in a form that is readable to humans and easily convertible for output (or to map into memory).

In issue #4, we dove into BCD, working with massive numbers in the process. Last month (issue #5), we used BCD to accumulate memory banking stats for the F256 Jr. platform in a bitmapped graphics memory banking use case (counting up to 100,000,000 per mem bank metric).

As simple as BCD is to use, connecting it to graphic data might appear unnatural, or at a minimum, non-trivial; but in fact, the opposite is true. Powers-of-two bit-shift operations and friendly memory alignment help make our job easier.

In this FLASH! feature, we discuss the code used in the telemetry subroutine of the 'balls' demo starting with the no-frills version. The assembly code on page 2 and 3 gets the job done, but there is always room for improvement.

## Creating and locating graphic source data

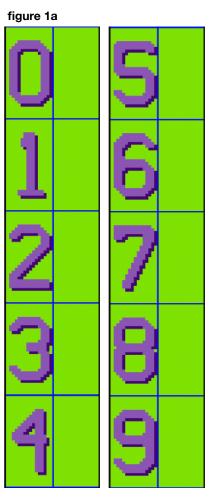

The set of purple on green sprites used in our demo was created using <u>ASEPRITE</u> in the form of a 32 x 352 pixel graphic image; in figure 1a, the '0..4', '5..9', and the comma are stacked end-to-end in memory, creating a tall column with a stride of 32 pixels (the blue ASEPRITE gridlines are for reference and do not exist in the data).

The workflow of: 'design' -> 'save' -> 'load' -> 'export' create Foenix load-ready sprite and color palette files, easily wrangled using 64TASS. As written, the compiler directives below pull data into our project starting at address \$8000. Omitting the '\* =' address will encode data *inline*, and we can move it later (we have a choice). In our code, we will point to it using the following low-byte/high-byte notation: '#<sprbmp' and '#>sprbmp'

\* = \$8000

sprbmp .binary "Sprite-10nums.data",0,11264

sprpal .binary "Sprite-10nums.data.pal",0,1024

Once data is where we need it, all that is required to instantiate is to set x and y locations, set the address (\$8000 in last months code) and set the sprite enable bit. (size, priority, and LUT defaults of 0 bring us across the finish line)

As luck has it, 32 pixels x 32 pixels is exactly 1,024 bytes, a size that we are pleased to work with since the offset between \$8000, \$8400, \$8800, etc. lends favorably to the simple shift & add algorithm covered on page 2.

All in all, the approach below is a "good enough is good enough" version and <u>is</u> the actual code present in the telemetry version of the balls demo published last month.

It performed well, but we had to limit the qty. of NBALLS rendered to 32.

Our next release will improve the design, cutting telemetry CPU use to a fraction (1/16th estimated).

In March, we will be publishing a "howto" guide (an easy to follow workflow) for adding your own bitmap data (or assets from elsewhere) into your programs using a low-cost option: ASEPRITE and a no-cost classic: GIMP (the Gnu Image Manipulation Program).

> Sprite set "Sprite-10numsv2" contains a few additional symbols

#### Code example 1 - telem01 (tallying counters with BCD math)

The code below represents the full end-to-end bank 'adder' subroutine which is used to accumulate 4 BCD digit pairs for a given (passed in via accumulator) bank number. We start by saving **a** (the accumulator) and in addition, push the x and y registers onto the stack because the calling code needs them back in the shape they sent them.

Unlike other CPUs, the 6502 is limited to only 3 'working' registers, necessitating store and load from memory. The trick is to orchestrate transfers between registers, the stack, and memory in a way that supports 'clean' code; otherwise known as *reliable*, *easy to follow*, and *adequately performant*.

Some of the VICKY I/O registers are write-only, but those that are read/write let us check state without using memory to manage (store and read); in other words, you can query and act on a value easily, and need not worry about drift.

But nothing is free; on the F256 platform, you are going to have to get used to managing I/O banks. This means establishing a policy to either keep the most oft accessed bank 'in' or alternatively, always set it based on 'need'. As an example, a text editor might opt to keep the *text* page banked in while a graphics or device-heavy use case might choose to keep the *I/O* bank resident.

If you read issue #4, you might recognize that the add #\$00 with carry methodology used below is similar to the De Jong code discussed in the Mersenne Prime example. This is a common way to conduct multi-byte addition (whether in BCD mode or standard, non-decimal base 2). The adc #\$00 seems peculiar, but is the 6502 'way' to add a carry bit forward.

Word of caution: the code below will *not* work on an old school 6502, since it uses the phx and phy opcodes which are 'new' to the WDC 65C02 (also available on

WDC 65C816 processors). If this were running on a Commodore 64 or PET, ATARI, or Apple, you would need to do the register shuffle; transfer y to a with tya; push from the accumulator to the stack; then commute x via txa, then push *that* to the stack, then do the reverse before returning. Bill Mensch and his friends were good enough to squeeze a few new opcodes and addressing modes into the WDC version of the classic MOS CPU.

This subroutine is called every time a bank is accessed in the xordraw ball loop (8x for each ball) otherwise known as quite frequently! Due to this heavy use, the 28 innocent-enough looking instructions chew up a pile of cycles in aggregate, so we short circuit the call to it when patching for non-telemetry mode.

Unfortunately, the calling code is located in a fairly tight code block which is not conducive to the patching method discussed in Issue #5; so our only option to disable without a test and branch statement is to overwrite the bytes at ptchpt1 (patch-point 1) with three nop opcodes. They are about 3x less expensive than a load, compare, branch and about 10x fewer cycles than running this gauntlet unconditionally.

This can be made slightly more efficient by removing the **bolded** decimal mode set and clear instructions below, but we are being courteous (for now) and leaving the modes and registers as we found them.

For this code to make sense, an understanding of the BANKCTR data structure is required. Simply, it is 32 bytes of memory or 8 sets of 4 byte counters where each 4 BCD bytes (when combined) can track up to qty. 8, base 10 digits of bank access; see the depiction in figure 2a and the on-screen representation in figure 2b. Note the transposition of BCD bytes between the two.

2

| telem01                                                                   | pha<br>phy<br>phx<br>asl a<br>asl a<br>tay                                                                                        | <pre>mult'ing a (passed in bank index) ; preserve a, y, x</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BANKCTR:<br>83 60 01 00 ; bank 0<br>; bank 1 (not shown)<br>; bank 2 (not shown)<br>; bank 3 (not shown)<br>; bank 4 (not shown) |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| The lone +1<br>math add                                                   | <pre>sed clc lda BANKCTR,y adc #1 sta BANKCTR,y iny lda BANKCTR,y adc #\$00</pre>                                                 | <pre>; set decimal mode<br/>; clear carry<br/>; load low-byte BCD pair otherwise known as (xx,xxx,x99)<br/>; add 1 we are here because a bank was retrieved<br/>; store back<br/>; get next BCD pair (xx,xx9,9xx)<br/>; add carry in case the prior went from 99 to 00</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ; bank 5 (not shown)<br>; bank 6 (not shown)<br>20 84 06 00 ; bank 7<br>figure 2a                                                |

| Each iny<br>Increments<br>index to the<br>more<br>significant<br>BCD byte | <pre>sta BANKCTR,y. iny lda BANKCTR,y adc #\$00 sta BANKCTR,y iny lda BANKCTR,y adc #\$00 sta BANKCTR,y cld plx ply pla rts</pre> | ; store it back<br>; same for (xx,99x,xxx)<br>; same for (99,xxx,xxx)<br>; same for (99,xxx,xxx)<br>; same for (fight definition of the state of th | 00016083<br>00068420<br>figure 2b                                                                                                |

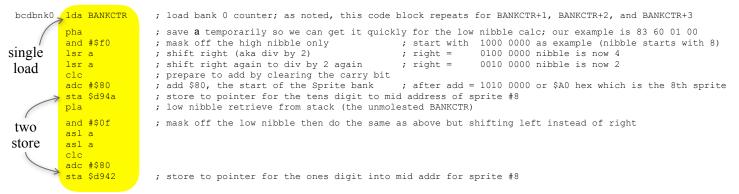

**Code example 2** - bcdbnk0 (converting from BCD values to sprite memory pointers)

This code example is the 2nd half of the equation. We are accumulating the totals above and do so in a neat, self-contained subroutine. The input to telem01 above is the bank #, and the routine manipulates the 32 byte BANKCTR data structure; otherwise, it minds its business.

Here (in bcdbnk0), we read from BANKCTR bytes and update the sprites which are already on the screen.

The phrase *data structure* (above) is being used loosely; there is no such thing in 6502 and most of the programmers I know typically do not bother with object notation or namespaces that some of the newer fangled assemblers now support. But acting as if you have C lang style structs and organizing memory and code with the tenets of higher level languages in mind can help large projects stay organized. : )

The primitive nature of 6502 assembly language places the onus to maintain order directly on the programmer. Absent are linters and compiler warnings, and CPU based memory protection does not exist in this universe.

We sit directly on hardware, coercing circuits to do things that fulfill and exceed the original CPU designer's dreams. Development is enjoyable because it is challenging. Cycle-optimized elegance is the reward.

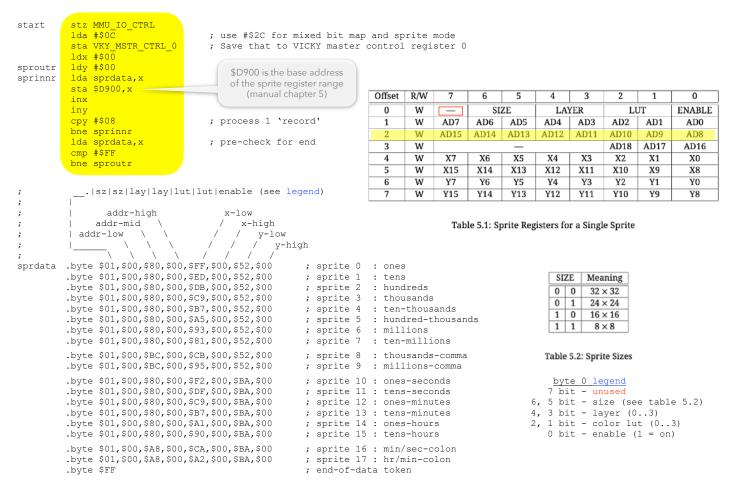

The following heavily commented code renders one pair of sprite numerals on-screen. Subsequent instances are identical, with the exception of the LDA (from BANKCTR in this case) and a pair of STA instructions (one per digit) to 'offset 2' of each sprite. (see the yellow highlight in table 5.1 on pg. 5 below) On pg. 6, you can see similar code to display digits of the onscreen TOD clock which is updated from an interrupt handler.

Table 5.1, from the F256 documentation, describes the sprite register format. The sprite address pointer is formed from 19 significant bits spread across 3 bytes. We only care about the middle byte and have initialized the high and low to 0 (see page 4). This will give us access to address in range of \$00:xx00

..... despite what looks like a 65C816 formatted 24 bit address, the F256 only uses 2 of the 3 high order bits to reach all of memory. We (mortals) cannot address more than 64K but VICKY can! We are pointing to offsets ('xx') that range from \$80 up through \$BC aka 16 sprites of 1K.

1

As discussed, each 8 digit counter represents one bank and each is ordered and encoded as 21 43 65 87. This is followed by the same sequence for bank 1, and so on.

This ordering may seem odd, but it is the nature of BCD to have the low nibble of each byte represent the lower order place (the ones place in "21") with the high nibble of the byte representing the 10's place or the 2 in "21". It's also the nature of loops and indexes (the y index, for example) to increment. Finally, it is the nature of 6502's little endian encoding to order low-to-high.

Indeed, processor addressing modes depend upon (require) low/high, and assemblers follow the rules; but much of the rest is convention. BCD is only concerned with adding two 8-bit values and will modify carry accordingly. That's it. It's as simple as it is brilliant.

In the screen shot in figure 2b, bank 0 counter = 16,083(padded zeros not reflected here) and bank 7 = 68,420.

If this were bank 0 and 1, BANKCTR memory would be ordered as follows: ~ ~ ~ ~ ~ ~ ~

|                         | 83 | 60 | 01 | 00 | 20 | 84 | 06 | 00 |  |

|-------------------------|----|----|----|----|----|----|----|----|--|

| This represents byte #: | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  |  |

... and this would continue three more times for a total of 32 bytes.

To repeat, the AND'ing, LSR'ing, and math to clear carry and add hex #\$80 in this implementation adjusts the middle byte of the 3 byte sprite pointer which, by design, begins at address of \$8000 and aligns to 0 byte boundaries. In the Mersenne prime example in issue #4, De Jong does something different; he adds #\$30 (48 decimal) to convert to ASCII, then prints to the screen using the kernel output of the mighty Rockwell AIM-65.

In a subsequent version of the balls demo, we will refactor 120 lines of code into just a handful of instructions but will *spend* a ton of memory using 128 sprite definitions. The result, from a performance perspective, will be greased lightning as compared to the original which is long and boring, but works.

We could go in the other direction and optimize for memory, using a table and indexed retrieval but that would require looping and additional cycles. Longer term, the aim is to gamify the demo and we will need the cycles for collision detection and more.

3

Code example 3 - sprload (sprite loader / copy routine: to load or not to load?)

There is nothing terribly innovative about the code below, but it is relevant in discussions focused on graphic data of one type or another. You've got data, your F256 is hungry for data, and you've got to load or move and store it and then tell VICKY where to find it.

The code is near identical to the character set 'load' routine that we used in the De Jong Mersenne Prime example in issue #4. In that program, we let 64TASS incorporate the old school Commodore PET font inline with our code and then copied it up into I/O bank 1 of \$C000. But let's start over.

The routine uses two pairs of zero page (low byte/high byte) addresses and exploits the indirect y-indexed addressing mode to move sprite data from a given location in memory to the desired destination (\$8000) that we depend upon in other parts of the program (the bcdbnk\* sprite pointing code discussed on page 3).

A mishap in this calculation will yield visual garbage (aka, the math in the above code to *not* point to the correct sprite, or to any sprite for that matter). Sometimes this is entertaining; most often, it's frustrating. A miscalculation can also be the cause of a nasty system crash or wild mishaps in cases where opcodes and data gets trampled upon.

Once the sprites are copied, we can use the memory it previously occupied to overlay code or to store and use other data. In the '80s, games such as *Space Taxi* would use this technique to load additional game levels and to maximize graphics and game code for a richer experience. Modern-vintage style games such as *Lair of the Lich King* by Micah Bly and *PETSCII Robots* by David Murray also use this technique. The bottom-left of page 1 illustrates an alternative; the "no-load" method. In this case, 64TASS assembler directives are used to align data with desired starting addresses. The assembler calculates and pads the object file to ensure alignment.

The benefit is we avoid having to write and execute code to perform data copy; the drawback is our binary file is potentially bloated. We did this in the original version of our balls demo which explains why our file size was a whopping 32K. At one end of the binary (\$8000, also the load address) was graphic sprite data; in the middle was the \$E000 machine code which included a modest amount of embedded table data; at the top end were 6502 vectors between \$FFFA-\$FFFF. All in all, 32K for the bouncing ball demo was wasteful, and I am sorry. : )

In a perfect world, we aim to organize our code, data, variables, and other assets so they reside in a tight blob\* of memory that can be loaded from storage, initialized, and executed with a minimum of fuss and resources. Usually, it's preferable to have a smaller file to load and code to relocate, where applicable. Initialization routines that perform the copy are usually faster than file load routines, even from SD Card. At least, that's the way it has been.

In our next version, we will load and locate larger chunks of graphic data using VICKY's DMA to do the heavy lifting; it is capable of moving many MB/sec. which is lightyears faster than a single-MHz. 8-bit CPU. For science, we will measure the time it takes to move 32K of data using standard 6502 instructions (the code below) versus using DMA. We will do this for science, because we can. We are computer scientists!

| 1<br>1<br>5<br>1 | da # <sprbmp<br>sta FROM_PTR<br/>da #&gt;sprbmp<br/>sta FROM_PTR+1<br/>da #\$80</sprbmp<br> | We load/copy pages<br>from: sprbmp<br>to: \$8000                                                                      |

|------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|                  | sta TO_PTR+1                                                                                | and stop at page <code>\$ac. The math is</code>                                                                       |

|                  | stz TO_PTR<br>.dv #\$00                                                                     | \$ac - \$80 (hex) = \$2c (hex) aka 44 decimal.                                                                        |

|                  | da (FROM PTR),y                                                                             | 44 divided by 4 pages of 256 = 11 (1K per sprite)                                                                     |

| s<br>i<br>k      | sta (TO_PTR),y<br>.ny<br>one sprloop                                                        | (but note, we start copying from a 0th page for sprite<br>#0; the final iteration of consequence, considering the     |

|                  | nc FROM_PTR+1                                                                               | ^2 math is the 10th for sprite # 10; 0 to 10 is 11                                                                    |

| 1                | .nc TO_PTR+1<br>.da TO_PTR+1<br>.mp #\$ac                                                   | The outer loop iterates and <i>then</i> tests/compare to \$ac.<br>The loop is actually copying from \$8000 to \$abff. |

|                  | one sprloop                                                                                 | , , , , , , , , , , , , , , , , , , , ,                                                                               |

| r                | rts                                                                                         |                                                                                                                       |

\* ... with the exception of the BASIC816 examples published in issues 1 through 3, all of our code has been in .bin 'blob' files. Shortly, we will be moving to <u>.PGX and .PGZ</u> files, the latter of which allows for multisegment relocation upon load. Until then, we will make believe it is still 1982 and move data to where we need it to be.

Here are the pointer definitions for FROM PTR and TO PTR. Note the.fill and the use of '?' instead of hard addresses.

| * = \$0<br>.fill<br>.dsection | 16<br>zp | ; reserved for MMU_MEM_CTRL (\$00) and MMU_IO_CTRL (\$01) plus MMU_MEM_BANK_0 through MMU_MEM_BANK_7<br>; declare section named "zp" aka zero page (from \$0; well from \$10 since we reserve 16 bytes) |

|-------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .section zp                   |          |                                                                                                                                                                                                         |

| FROM_PTR<br>TO_PTR            |          | ; two bytes which will be our low-byte / high-byte pair<br>; same                                                                                                                                       |

| BLNKFLG<br>BANKCTR            | .byte ?  | ; blinking colon state                                                                                                                                                                                  |

| .fill<br>.send                | 32       | ; 32 byte 'data structure'<br>; zp (zero-page) section end                                                                                                                                              |

Code example 4 - sprinit (initializing graphics mode and sprites)

In this example we configure VICKY's master control register to enable sprite graphics then populate registers for 18 sprites in the process, re-using some of the digit placement data from the bank counters of issue #5's demo. We also prepare for RTC display; specifically, the time-of-day, replacing the bank 7 counter with colon delimited digit pairs.

In 'balls', sprite registers were populated through a lengthy sequence of fall-through immediate mode load and store instructions. Here, we pull sprite config data from .byte statements using a loop to increment sprite-by-sprite until a \$FF is found in the first column of the table. Since bit 7 of byte 0 is **unused** (see the legend beneath table 5.2), the existence of this value will not occur in normal use. The commented source and table 5.1 below, covers the rest.

The Foenix Marketplace contains a single .zip file containing the source, assembled binary, and an *updated* sprite set (a few special symbols are added to the original set of numerals; the original comma has been shifted from the 11th position to the 16th to preserve the natural ASCII order of a subset of the special symbols for which the all important ':' is part of)

We are angling to tie the RTC periodic interrupt timer to query the time-of-day of the RTC, itself. The "PIE" periodicinterrupt-enable bit turns on this function, obeying the "RS" rate nibble which can be set from 500 ms. all the way down to  $30.5175 \,\mu$ s. (microseconds). The fact that we are notified every 1/2 second comes in handy not just because it's a reasonable interval to update the clock, but because it provides a lever to use an extremely simple piece of code to flash the ':' sprites between the digit pairs.

The Texas Instruments <u>bq4802</u> does most of the work, but VICKY integrates the clock ICs signaling into its interrupt scheme and maps the R/W registers into memory on the I/O page of C000 at documented addresses.

The use of IRQ handlers for graphics versus device servicing purposes is a broad topic and we won't do it justice here; but to preface the conversation, sometimes a use-case calls for deterministic time intervals, useful for graphics and game action; other times, IRQs are used to read device queues to prevent overflow conditions. The WDC 65C22 circuit also has timers that we can use for interrupts, but the RTC is easy and reliable.

Operating systems have multiple interrupts active simultaneously and yet, the 6502 has but a single interrupt request line, so how is this managed? Again, VICKY "to the rescue"; as you will see on pg. 6, she manages over a dozen interrupts across 3 bytes worth of mask and pending bits, so we can specify which event(s) will even bother the IRQ line and once triggered, identify the responsible party. In the 'no-kernel' model, we commandeer the entire machine but mask and check 'pending' as if there *might* be other interrupts in use; it is good practice to do so.

5

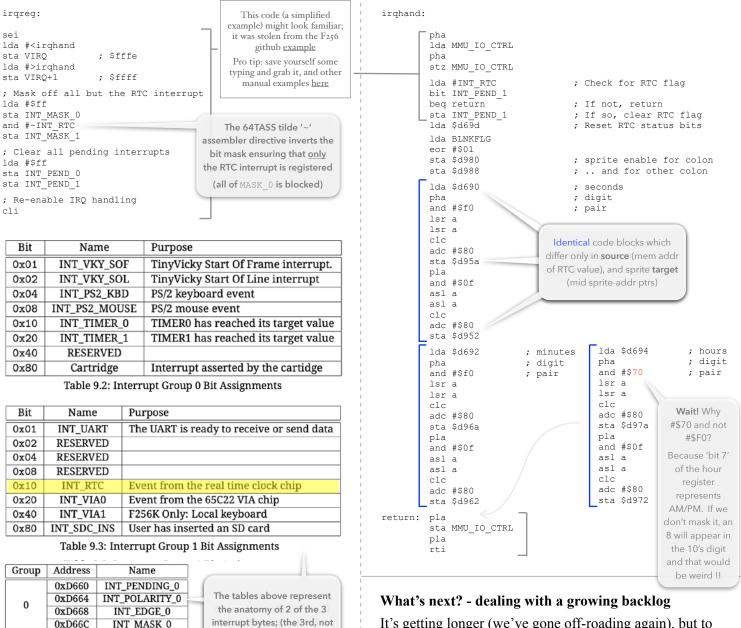

#### Code example 5 - irqreg and irqhand (real time clock interrupt registration and handler)

The code on the left installs the handler, masking all but the RTC interrupt; the code on the right is the handler itself, and does three things: a) checks to see if the interrupt is a result of the RTC timer (and not a spurious serial port or PS/2 interrupt); it b) toggles two sprite enable bits leveraging the eor instruction; and c) clears the interrupt and reads the RTC status bit, thus clearing its trigger in order to get ready for the next. For more information, see the article on setting the RTC on the C256U+ by Ernesto Contreras (issue #3) and Peter Weingartner's F256 manual (chapter 10 - tracking time).

It's getting longer (we've gone off-roading again), but to join a few threads together, the following represents bestcurrent-thinking of how to bridge recently discussed topics.

We covered item 'i.' (The RTC) above but still need to address issue #4's 'g.' (keyboard input) along with item 'k.', which revisits redefined characters - "VIC-20 style"; So the early March feature will be focused on the PS/2 keyboard.

After that, we will discuss graphic (sprite and bitmap) workflow and then pickup the Flash! issue #5 'balls' demo and item 'l.' (reading ATARI style joysticks) with some of the discussed telemetry enhancements and a low (no) budget gamification of a platform classic, just in time for <u>VCF East, April 14-16</u>. At least that's the plan for now!

6

Table 9.1: Interrupt Registers

INT\_PENDING\_1

INT\_POLARITY\_1

INT\_EDGE\_1

INT\_PENDING\_2

INT\_POLARITY\_2

INT EDGE 2

INT\_MASK\_2

INT\_MASK

0xD661

0xD665

0xD669

0xD66D

0xD662

0xD666

0xD66A

0xD66E

1

2

| Address | R/W | Name          | 7     | 6                | 5 | 4              | 3               | 2    | 1        | 0 |  |

|---------|-----|---------------|-------|------------------|---|----------------|-----------------|------|----------|---|--|

| 0xD690  | R/W | Seconds       | 0     | second 10s digit |   |                | second 1s digit |      |          |   |  |

| 0xD691  | R/W | Seconds Alarm | 0     | second 10s digit |   |                | second 1s digit |      |          |   |  |

| 0xD692  | R/W | Minutes       | 0     | minute 10s digit |   |                | minute 1s digit |      |          |   |  |

| 0xD693  | R/W | Minutes Alarm | 0     | minute 10s digit |   |                | minute 1s digit |      |          |   |  |

| 0xD694  | R/W | Hours         | AM/PM | 0                |   | hour 10s digit |                 | hour | 1s digit |   |  |

shown, includes 4 bits for

low level IEC control and

The table to the left details

memory addresses and the

PENDING and MASK bytes

leveraged in our code.

data lines)

Table 10.2: Real Time Clock Registers